# VHDL, Verilog and Advanced Verilog

# Umabalaji, Assistant Professor/ECE, SCSVMV

# December 2020

# 1 Aim

The high level programming languages permit complex design concepts to be communicated as computer programs likewise VHDL permits the behavior of complex electronic circuits to be captured into a design system for automatic circuit synthesis or for system simulation.

# 2 Purpose of VHDL and Verilog

- It is a hardware description language used in electronic design automation to describe digital and mixed signal systems such as Field Programmable Gate Arrays(FPGA) and integrated circuits.

- It is very helpful to think in the view of gates and flip-flops but not as variables or functions.

- It is helpful to know about which part of the circuit is combinatorial and which part is sequential.

# 3 Why to use an HDL

- It is beneficial to describe problems and faults in the design before implementing it in hardware.

- It is very appropriate to build a prototype of the circuit previously to

its manufacturing process because the complexity of an electronic circuit

grows exponentially.

- It makes easy for a team of developers to work together.

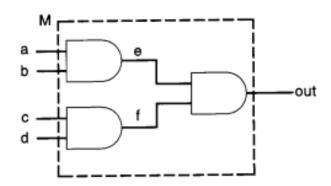

# 4 How to describe a structure

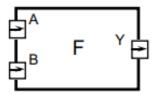

A digital electronic system can be described as a module with inputs and/or outputs.

In the above diagram, the module F has two inputs A and B and an output Y, which means to say that electrical values on the outputs are some function of the values on the inputs. We specify the module F as a design entity and the inputs and outputs are called ports.

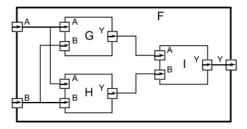

It is very easy to describe the function of a module i.e. how it is composed of sub-modules. Each of the sub-modules is an instance of some entity and the ports of the instances are connected using signals.

The above diagram describes the structural view of description which shows how the entity F might be composed of instances of entity G,H and I. Overall(main) module is F which has two inputs A and B. There are three submodules G,H and I. In many cases, it is not relevant to describe a module structurally. In such cases, a description of the function performed by the module is required, without reference to its actual internal structure. Such a description is called behavioural or functional description.

For example, Consider F modules as a XOR Gate. Then the behavioural description of a F could be a Boolean expression.

$$Y = A \cdot B + A \cdot B$$

In the above exclusive-OR equation, the first sub-module(G) is going to describe the first function A.B and the second sub-module(H) is going to describe the second function A.B. Then both the sub-modules are going to be added in the third sub-module(I). Eventually, the output will be coming out as a function Y which A.B+A.B.

# 5 Pre MCQ

1. What does a decimal number represents?

|    | <ul><li>a) Quality</li><li>b) Quantity</li><li>c) Position</li><li>d) None of the above</li></ul>                                                                                                              |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Binary numbers can be converted into equivalent octal numbers by making groups of three bitsa) Starting from the MSB b) Starting from the LSB c) Ending at the MSB d) Ending at the LSB                        |

| 3. | What is the octal equivalent of $58$ ?<br>a) $010_2$<br>b) $110_2$<br>c) $000_2$<br>d) $101_2$                                                                                                                 |

| 4. | What is the hex equivalent of 916?<br>a) $1111_2$<br>b) $1001_2$<br>c) $0110_2$<br>d) $1100_2$                                                                                                                 |

| 5. | Which one is the possible technique for representing signed integers?  a) Signed Magnitude representation b) Diminished Radix-complement representation c) Radix-Complement representation d) All of the above |

| 6. | What are the two ways of representing the 0 with signed magnitude representation? a) -0 and -0 b) +0 and +0 c) -0 and +0 d) None of the above                                                                  |

| 7. | 2's complement is used to represent signed integers, especially integers.                                                                                                                                      |

|     | <ul> <li>a) Negative</li> <li>b) Positive</li> <li>c) Both A and B</li> <li>d) None of the above</li> </ul>                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.  | For subtraction of binary number, subtract thea) Minuend from the subtrahend b) Subtrahend digit from the minuend c) MSB from the LSB d) None of the above |

| 9.  | Floating-point numbers are those numbers which includea) Decimals b) Fractional parts c) Integer values d) All of the above                                |

| 10. | Binary coded decimal or BCD is also known as a) 2841 b) 4821 c) 4281 d) 8421                                                                               |

| 11. | what is the decimal representation of decimal number 5? a) 0000 b) 1001 c) 0011 d) 0101                                                                    |

| 12. | EXOR is the of the binary number. a) MSB to the next bit b) LSB to the next bit c) MSB of the previous bit d) LSB of the previous bit                      |

| 13. | Which sign bit is used for representing the positive sign in floating point representation. a) 0 b) 1 c) either a or b d) None of the above                |

| 14. | A basic AND gate consists of inputs and an output a) One b) Zero c) Two d) Ten                                                                                  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15. | For multiple-input AND and NAND gates, the unused input pin should not be left a) ON b) Connected c) Unconnected d) None of the above                           |

| 16. | When a logic circuit diagram is given,<br>You can analyze the circuit to obtain the a) Result b) Input c) Logic Expression d) None of the above                 |

| 17. | Boolean algebra is named after, who is used it to study human logical reasoning a) Anderson,Mary b) Acharya Kanad c) Dickson,Earle d) George Boole              |

| 18. | A is a table, which consists of every possible combination of inputs and its corresponding outputs.  a) Last table b) Truth table c) K-Map d) None of the above |

| 19. | Canonical form is a unique way of representinga) SOP b) Minterm c) Boolean expressions d) A Page                                                                |

| 20. | It is a simple combinational digital circuit built from logic gates                                                                                             |

a) Full adder

- b) Half adder

- c) Null adder

- d) None of the above

- 21. In a circuit, which subtracts two inputs each of one bit

- a) Full subtractor

- b) Full adder

- c) Half subtractor

- d) All of the above

- 22. It is the converse of decoding and contains 2n(or fewer) input lines and n output lines

- a) Subtractor

- b) Decoder

- c) Multiplexer

- d) Encoder

- 23. It is a very useful combinational circuit used in communication systems

- a) Parity Bit checker

- b) Parity Bit Generator

- c) Both A and B

- d) Parity Bit

- 24. It compares two n-bit values to determine one of them is greater or if they are equal

- a) Calculator

- b) Multiplexer

- c) Comparator

- d) None of the above

- 25. It is a circuit, which has a number of input lines and selection lines with one output line

- a) Sequential circuit

- b) Multiplexer

- c) Counter

- d) All of the above

- 26. It is a circuit, which can remember values for a long time or change values when required

- a) Ripple

- b) Counter

- c) Circuit

|     | d) Memory element                                                                                                                                                                                                                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27. | It is a sequential circuit that cycles through a sequence of states a) Multiplexer b) Demultiplexer c) Counter d) Ripple                                                                                                                         |

| 28. | it is a counter where the flip-flops do not change states at exactly the same time, as they do not have a common clock pulse a) Asynchronous Ripple counter b) Synchronous Ripple counter c) Counter d) None of the above                        |

| 29. | It is a bi-directional counter capable of counting in either of the direction depending on the control signal a) Up Synchronous Counter b) Down Synchronous Counter c) Synchronous Counter d) All of the above                                   |

| 30. | In this logic, output depends not only on the current inputs but also on the past input values. It needs some type of memory to remember the past input values a) Logical circuit b) Connected circuit c) Sequential circuit d) Parallel circuit |

| 31. | There are two types of parity, a) Even b) Odd c) First d) Both (a) and (b)                                                                                                                                                                       |

| 32. | Decoders often come with an enable signal, so that the device is only activated when the enable equals to a) 2 b) 1 c) 3                                                                                                                         |

|     | d) Either (a) or (b)                                                                                                                                                         |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33. | When more than one input can be active, the priority must be used. a) Terms b) Words c) Encoder d) None of the above                                                         |

| 34. | The characteristics equation of any flip-flop describes the of the next state in terms of the present state and inputs.  a) Impact b) Behavior c) Path d) None of the above. |

| 35. | The normal data inputs to a flip-flop(D, S and R, J and K, T) are referred to as inputs. a) Sequential b) Synchronous c) Asynchronous d) Both (a) and (b)                    |

| 36. | A PLA consists of two-level circuits on a single chip. a) AND-OR b) NOR-NAND c) XOR-AND d) OR-AND                                                                            |

| 37. | It is a single input version of JK Flip-flop formed by typing both the inputs of JK.  a) D Flip-flop b) S Flip-flop c) T Flip-flop d) N Flip-flop                            |

| 38. | In flip-flop the arrow shows positive transition on the clock a) Upward b) Downward c) Vertical d) Horizontal                                                                |

| 39 | <ul> <li>a) Logic gates</li> <li>b) Registers</li> <li>c) ROM</li> <li>d) None of the above</li> </ul>                                                                                                                                      |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40 | <ul> <li>A register can also be used to provide data movements.</li> <li>a) Parallel Register</li> <li>b) Simple Register</li> <li>c) Shift Register</li> <li>d) All of the above</li> </ul>                                                |

| 4  | <ul> <li>a) Six</li> <li>b) Four</li> <li>c) One</li> <li>d) Many</li> </ul>                                                                                                                                                                |

| 42 | <ul> <li>2. In this type of counter, the output of the last stage is connected to the D input of the first stage.</li> <li>a) Ring counter</li> <li>b) Johnson counter</li> <li>c) Straight counter</li> <li>d) All of the above</li> </ul> |

| 4; | 3. A device that exhibits two different stable states and functions as memory element in a binary system is known as a) Registers b) Flip-flops c) VLSI d) Both (b) and (c)                                                                 |

| 4  | <ul> <li>4 organization is essentially an array of selectively open and closed unidirectional contacts.</li> <li>a) ROM</li> <li>b) RAM</li> <li>c) Computer</li> <li>d) All of the above</li> </ul>                                        |

| 4  | <ul><li>5. A memory stores data for processing and the instructions for</li><li>a) Result</li><li>b) Execution</li></ul>                                                                                                                    |

|     | c) Process d) All of the above                                                                                             |

|-----|----------------------------------------------------------------------------------------------------------------------------|

| 46. | Half adder consists of & gates. a) EX-OR & AND b) EX-OR & OR c) EX-OR & NOT d) None of this                                |

| 47. | are used for converting one type of number system into another form.  a) Encoder b) Logic gate c) Half adder d) Full adder |

| 48. | A register is a group ofa) OR gates b) OR & AND gates c) Flip-flops d) None of these                                       |

| 49. | A flip-flop has stable states. a) Two b) Three c) Four d) Five                                                             |

| 50. | It does not have any external gate. a) Simple Register b) Buffers                                                          |

# 6 Prerequisite

c) Memory d) RAM

- The prerequisite for VHDL programming are the fundamentals of digital electronics and digital circuit design.

- To fully understand the VHDL programs, it is very important to have adequate knowledge of Boolean algebra, logic gates, combinational and sequential logic gates

# 7 VHDL Content

# 7.1 Introduction

Very High Speed Integrated Circuit(VHSIC) is a language for describing digital electronic systems and was initiated at 1980. It is very clear that always there was a need for a standard language for describing the structure and function of Integrated Circuits(ICs). Hence it was developed and approved as a standard by the Institute of Electrical and Electronic Engineers(IEEE) in the US.

VHDL is specifically originated to fulfill certain design needs in the entire design process.

- 1. HDL provides description of the structure of a design i.e. how it is decomposed into sub-designs.

- 2. It provides the specification of the function of design using familiar programming language forms.

- 3. Very importantly, it provides a design to be simulated before being manufactured, so that designers can quickly compare alternatives and test for correctness without the delay and expense of hardware prototyping.

It is a hardware description language which uses the syntax of ADA. It is used for many applications like for describing hardware, as a modeling language, for simulation of hardware, for early performance estimation of system architecture, for synthesis of hardware, for fault simulation, test and verification of designs.

It has been designed and optimized for describing the behavior of digital circuits and systems. It combines features of the following:

- A simulation modeling language

- A design entry language

- A test language

- A netlist language

- A standard language

# 7.2 How is VHDL used?

It is a general purpose programming language optimized for electronic circuit design. As such, there are many points in the overall design process at which VHDL can help.

• **Design Specification** - HDL plays a major role in to capture the performance and interface requirements of each component in a large circuit. Using a top-down approach to design, a system designer may define the

interface to each component in the system, and describe the acceptance requirements of those components in the form of a high-level test bench. The interface definition (typically expressed as a VHDL entity declaration) and high-level performance specification (the test bench) can then be passed on to other team members for completion or refinement.

- Design capture It is a phase in which the details of the system are entered in a computer based design system. In this phase, you may express your design (or portions of your design) as schematics (either board-level or purely functional) or using VHDL descriptions. The design capture phase may include tools and design entry methods other than VHDL. In many cases, design descriptions written in VHDL are combined with other representations, such as schematics, to form the complete system.

- For design simulation Once entered into a computer based system design, it will be easy to simulate the operation of a circuit to find out if it will meet the functional and timing requirements developed during the specification process.

- **Design Documentation** The structured programming features of VHDL, coupled with its configuration management features, make VHDL a natural form in which to document a large and complex circuit. The value of using a high-level language such as VHDL for design documentation is pointed out by the fact that the U.S. Department of Defense now requires VHDL as the standard format for communicating design requirements between government subcontractors.

- As an alternative to schematics Schematics have long been a part of electronic system design, and it is unlikely that they will become extinct anytime soon. Schematics have their advantages, particularly when used to depict circuitry in block diagram form. For this reason many VHDL design tools now offer the ability to combine schematic and VHDL representations in a design.

- As an alternative to proprietary languages Proprietary languages such as PALASM, ABEL, CUPL and Altera's AHDL have been developed over the years by PLD device vendors and design tool suppliers, and remain in widespread use today. In fact, there are probably more users of PLD-oriented proprietary languages in the word today than all other HDLs (including Verilog and VHDL) combined.

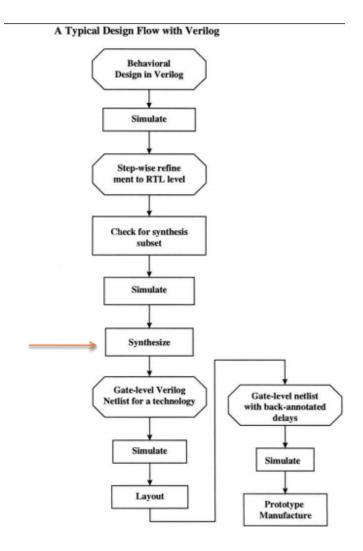

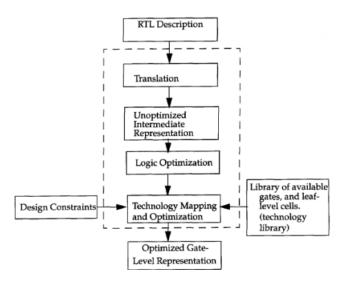

# 7.3 VHDL Design flow

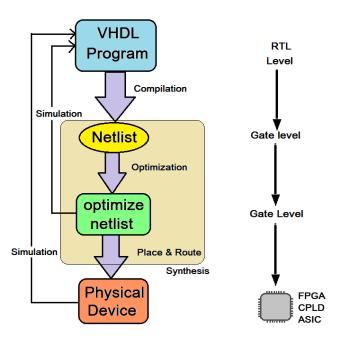

- The Design flow starts with writing a HDL code of your circuit design. There are various companies in the market like XILINX, Altera etc. provide their own software development tools to edit, compile and simulate the HDL code and eventually the circuit is described in RTL at this level.

- The compiled HDL code generates netlist at Gate level. Especially, the compiler in the tool high-level VHDL code in RTL to Gate level.

- The generated netlist is further optimized to get netlist again at gate level and the simulation of the design is done at this stage.

- Finally a physical device is implemented on CPLD/FPGA from this optimized netlist. Once again the final device can be simulated and verified.

# 7.4 VHDL program Structure

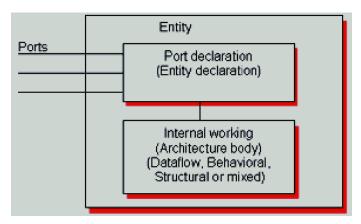

- All the VHDL program consists of two components Entity and Architecture

- It may have additional components like configuration, package declaration, body, etc. as per requirements.

# The structure of the program is:

```

LIBRARY library name;

use library_name.package_name.package_parts;

ENTITY entity_name IS

PORT(port name : port_mode port_type;

PORT(port name : port_mode porttype;

.

.

.

.

.

.

.

.

.

.

ARCHITECTURE archi_name of entity_name is declarations

BEGIN

code(sequential or concurrent statements)

.

.

.

.

.

END archi_name;

```

# 7.5 Entity and Architecture

To describe the entity, VHDL provides five different types of primary constructs, called design units.

They are:

- 1. Entity declaration

- 2. Architecture body

- 3. Configuration declaration

- 4. Package declaration

- 5. Package Body

- 1. **Entity declaration** It describes the external view of the entity. For example, the input and output signal names.

- 2. **Architecture body** It contains the internal description of the entity. For example, a set of concurrent or sequential statements that represents the behavior of the entity.

- 3. Configuration declaration It is mainly used to create a configuration for an entity. It specifies the binding of one architecture body from the many architecture bodies that may be associated with the entity. Also specifies the bindings of components used in the selected architecture body to other entities.

- 4. **Package declaration** It confined with a set of related declarations, such as type declarations, subtype declarations, and subprogram declarations, which can be shared across two or more design units.

- 5. **Package body** It contains the definitions of subprograms declared in a package declaration.

# 7.5.1 Very simple Entity declaration and Architecture Body

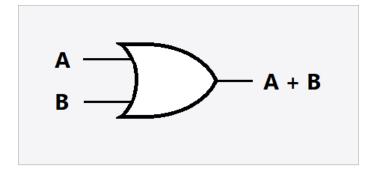

Using an OR gate, we can see how the entity is declared. Here in this diagram,

the OR gate has two inputs and one output. So the entity has totally 3 input and output signals.

```

A \& B = input signals

Y(A+B) = output signal

```

As per the VHDL program structure, the entity declaration for the above OR gate will be,

```

\begin{array}{l} \text{entity } OR\_\text{gate is} \\ \text{port}(A,\!B: \text{in std\_logic}; \, Y: \text{out std\_logic}); \\ \text{end } OR\_\text{gate}; \end{array}

```

For the same OR gate, let us conclude the architecture body,

```

architecture dataflow of OR-gate is begin Y \le A AND B; end dataflow;

```

The above is the very simple explanation of the VHDL code as per the program structure. We can verify this coding by using the truth table of OR gate. Similar way, the same can be applicable to all the digital logic concepts.

# 7.6 Types of modelling in VHDL

There are three modelling styles are available in VHDL.

- 1. Dataflow Modelling

- 2. Behavioral Modelling

- 3. Structural Modelling

An architecture can be written in one of these three basic coding styles. The difference between these styles is based on the type of concurrent statements used:

- A dataflow architecture uses only concurrent signal assignment statements.

- A behavioral architecture uses only process statements

- A structural architecture uses only component instantiation statements

It is also preferable to go with mixed style of modelling to express the digital concepts in the programmer's view.

# 7.6.1 Behavioral Modeling

Behavioural modeling describes the highest level of abstraction in the circuit design using VHDL, where the circuit to be designed is described in terms of behaviour of output in response to the changes in the input. It describes a circuit at a functional level. It is a sequential style of modeling wherein a sequence of statements are available in this. In this behavioral modeling let's see the explanation of process statement which is the major syntax.

#### Process statement

It contains sequential statements that express the functionality of a portion of an entity in sequential terms.

# Syntax of process statement

```

[process-label:] process [(sensitivity-list)] [is] process-item-declarations

```

#### begin

sequential-statements;

(variable-assignment-statement

signal-assignment-statement

wait-statement

if-statement

case-statement

loop-statement

null-statement

exit-statement

next-statement

assertion-statement

report statement

procedure-call-statement

return-statement

end process [process-label];

A set of signals to which the process is sensitive is defined by the sensitivity list. Exactly, each time an event occurs on any of the signals in the sensitivity list, the sequential statements within the process are executed in a sequential order, that is, in the order in which they appear. Eventually, the process statement suspends after executing the last sequential statement and will wait for another event to occur on a signal in the sensitivity list.

#### For example

architecture behavior of ent is begin

```

\begin{aligned} & \operatorname{process}(A,B,C,D) \\ & \operatorname{variable}\ t1,t2:BIT; \\ & \operatorname{begin} \\ & t1 := A \ \operatorname{and}\ B; \\ & t2 := C \ \operatorname{and}\ B; \\ & t1 := t1 \ \operatorname{or}\ t2; \\ & Z <= \ \operatorname{not}\ t1; \\ & \operatorname{end}\ \operatorname{process}; \\ & \operatorname{end}\ \operatorname{behavior}; \end{aligned}

```

In the above example, the process statement has four signals in its sensitivity list and one variable declaration. If an event occurs on any of the signals A,B,C,D, the process is executed, then one by one statement is executed until the process suspends and wait for another event to occur on a signal in the sensitivity list.

# Variable Assignment Statement

In this assignment statement, the variables can be declared and used inside a process statement. It has the form

```

variable-object := expression;

```

This expression is evaluated when the statement is executed and the computed value is assigned to the variable object instantaneously. Variables are created at the time of elaboration and retain their values throughout the entire simulation run. This is due to the process is never excited, it will be either in an active state or in a suspended state for an event to occur.

Signal Assignment Statement Here in this, signals are assigned values using a signal assignment statement.

The general form is

# signal-object <= expression [ after delay-value];

It can appear either inside or outside the process statement. If it occurs outside, it is contemplated to be a concurrent signal assignment statement, perhaps, if it occurs inside a process, it is contemplated to be a sequential signal assignment statement and is executed in sequence w.r.t other sequential statements which appear within that process.

When a signal assignment statements is executed, the value of the expression is computed, and this value is scheduled to be assigned to the signal after the specified delay.

## For example

```

counter \le counter + "0010";

```

Assign after a delay

# Wait Statemenet

This provides an alternative way to suspend the execution of a process. Basically, there are three forms of the wait statement.

```

wait on sensitivity-list;

wait until boolean-expression;

wait for time-expression;

```

The above all the three can be combined in a single wait statement, like,

wait on sensitivity-list until boolean-expression for time-expression;

```

For example

wait on A,B,C;

wait until A=B;

```

The execution of the wait statement in the first statement causes the enclosing process to suspend and then wait for an event to occur on signal A,B or C. Once that happens, the process resumes execution from the next statement onwards.

#### IF statement

It selects the sequence of statements for execution based on the value of a condition. The condition can be any expression that evaluates to a Boolean value. The general form of an if statement is

```

if boolean-expression then

sequential-statements

{ elsif boolean-expression then

sequential statements }

else

sequential-statements

end if:

```

This is executed by checking each condition sequentially until the first true condition is found; then, the set of sequential statements associated with this condition is executed. The if statement can have zero or more elsif clauses and an optional else clause. It is also a sequential statement, therefore the arbitrary nesting of if statements are allowed as given in the above general form.

#### For example

```

\begin{aligned} & process(CLK, \, RESET) \\ & begin \\ & if \, RESET = \, '1' \, then \end{aligned}

```

```

COUNT <= 0;

elseif CLK'event and CLK='1' then

if (COUNT ¿= 9) then

COUNT ¡= 0;

else

COUNT ¡= COUNT + 1;

end if;

end process;

```

#### Case Statement

It selects one of the branches for execution based on the value of the expression. The expression value must be of a discrete type or of a one-dimensional array type. Choices may be expressed as single values, as a range of values or by using the others clause. The general form of this is

```

case expression is

when choices => sequential-statements

when choices => sequential-statements

when others => sequential-statements

end case;

```

# For example

```

case SEL is when "01" => Z <= A; when "10" => Z <= B; when others => Z <= 'X'; end case;

```

# NULL statement

It is a sequential statement that does not cause any action to take place, execution continues with the next statement. The general form is null

#### Loop Statement

It is used to iterate through a set of sequential statements. The general form is

```

[loop-label:] iteration-scheme loop sequential-statements end loop[loop-label];

```

There are three different iteration schemes. The first is the **for** iteration scheme, which has the general form

for identifier in range

# For example

```

\begin{array}{l} {\rm process}\;(A)\\ {\rm begin}\\ {\rm Z}<="0000";\\ {\rm for}\;i\;{\rm in}\;0\;{\rm to}\;3\;{\rm loop}\\ {\rm if}\;(A=i)\;{\rm then}\\ {\rm Z}(i)<='1';\\ {\rm end}\;{\rm if};\\ {\rm end}\;{\rm loop};\\ {\rm end}\;{\rm process}; \end{array}

```

The second form of the iteration scheme is the  ${\bf while}$  scheme, which has the form

while boolean-expression

#### For example

```

J := 0; SUM := 10; WH\_Loop: while J < 20 loop SUM := SUM 2; J := J+3; end loop;

```

The third form of the iteration scheme is one where no iteration scheme is specified. In this form of loop statement, all statements in the loop body are repeatedly executed until some other action causes the loop to exit. This can be done by an exit statement, a next statement, or a return statement.

# Exit statement

It is a sequential statement that can be used only inside a loop.

```

exit [loop-label] [when condition];

```

# For example

```

loop

wait on A,B;

exit when A=B;

end loop;

```

# Next statement

This one is also a sequential statement that can be used only inside a loop.

```

next [loop-label] [when condition];

```

This statement results in skipping the remaining statements in the current iteration of the specified loop; execution resumes with the first statement in the next iteration of this loop, if one exists. If no loop label is specified, the innermost loop is assumed. The exit statement will terminate the operation but in contrast with that the next statement causes the current loop iteration of the specified loop to be prematurely terminated and execution resumes with the next statement.

# For example

```

for I in 0 to 7 loop

if SKIP = '1' then

next;

else

NBUS <= TABLE(I);

wait for 5 ns;

end if;

end loop;

```

### **Assertion Statement**

These are useful in modeling constraints of an entity. For example, if we want to check some signal values which can lies within a specified range, or check the setup and hold times for signals arriving at the inputs of an entity, if the check fails, a message is reported.

```

The general form is

assert boolean-expression

{ report string-expression }

{ severity expression};

```

If the value of the Boolean expression is false, the report message is printed along with the severity level. The expression in the severity clause must be a value of type SEVERITY-LEVEL. The severity level is typically used by a simulator to initiate appropriate actions depending on its value.

# Report statement

This can be used to display a message. It is similar to an assertion statement, but without the assertion check. The general form is

```

report string-expression

severity expression

```

The expression in the severity clause, if present, must be of the pre-defined type SEVERITY\_LEVEL. If not present, the default severity level of NOTE is used.

# 7.6.2 Dataflow Modeling

This kind of modeling absolutely conveying about a system in terms of how data flows through the system. Data dependencies in the description match those in a typical hardware implementation. It directly implies the corresponding gatelevel implementation. It consists of one or more signal assignment statements. This style is very nearest to RTL description of the circuit.

One of the essential technique for modeling the dataflow is using the **concurrent signal assignment** statement. The architecture body definitely contains at least single concurrent signal assignment statement that represents the dataflow of the signal.

The elucidation of this concurrent signal assignment statement is that whenever there is an event (a change of value) on either signal, For example the program contains only A and B, then the expression on the right side is evaluated.

Event on (A) or (B) = evaluation on the right side

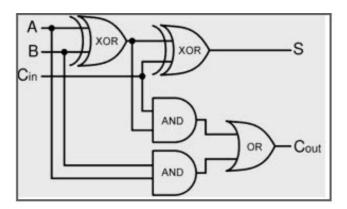

Let us consider the example of Full adder.

Here, there are 3 inputs & 2 outputs and 2 XOR gates, 2 AND gates & 1

OR gate.

Let us consider the boolean equation of a full adder is,

```

S = A \ XOR \ B \ XOR \ Cin Cout = (A \ AND \ B) \ OR \ (B \ AND \ Cin) \ OR \ (Cin \ AND \ A)

```

The above equation can be used to write the VHDL program for a full adder simply to express that concurrent signal assignment statements are executed whenever events occur on signals that are used in their expressions.

Two signal assignment statements (S and Cout) are used to represent the dataflow of the full adder entity. Whenever an event occurs on signals A,B or Cin, expressions of both statements are evaluated. The dataflow model for a 1-bit full adder using VHDL is,

```

entity full_adder is

port(A,B,Cin: in Bit; S,Cout:out Bit);

end full_adder;

architecture fa of full_adder is

begin

S <= A xor B xor Cin;

Cout <= (A and B) or (B and Cin) or (Cin and A);

end fa;

```

It is very substantial to note down that whether the signal assignment statement is inside or outside the process statement.

- The signal assignment statement inside the process statement is called sequential signal assignment statement.

- while the signal assignment statements that appear outside of a process are called concurrent signal assignment statements.

Concurrent signal assignment statements are event-triggered, that is, they are executed whenever there is an event on a signal that appears in its expression.

Sequential signal assignment statements are not event-triggered and are executed in sequence in relation to the other sequential statements that appear within the process.

In some cases, each concurrent signal assignment statement creates a driver for the signal being assigned. We should look after when there is more than one assignment to the same signal. In these cases, the signal has more than one driver(process that assigns values to the signal) and a specific mechanism is needed to compute the effective value of the signal.

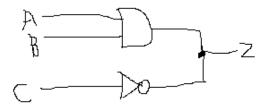

In this diagram, we have one AND gate(with two inputs) and one NOT gate. There are 3 drivers for signal Z. How is the value of Z determined? It is resolved by using a user-defined resolution function that considers the values of both the drivers for Z and determines the effective value.

Consider the following architecture body

```

architecture example1 of archi is begin Z <= '1' after 2ns,'0' after 5ns,'1' after 10ns; Z <= '0' after 4ns, '1' after 5ns, '0' after 20ns; Z <= '1' after 10ns, '0' after 20ns; end archi;

```

Each driver has a sequence of transactions where each transaction defines the value to appear on the signal and the time at which it is to appear. The resolution function resolves the value for the signal Z from the current value of each of its drivers.

The very interesting concept in VHDL is the **conditional Signal Assignment Statement**. It selects different values for the target signal based on the specified, possibly different, conditions. It is like an if statement in major high level programming languages.

Whenever an event occurs on a signal used in either any of the waveform expressions or any of the conditions, the conditional signal assignment statement is executed by evaluating the conditions one at a time.

# Example

```

Z \le IN0 after 10ns when S0 = '0' and S1 = '0' else IN1 after 10ns when S0 = '1' and S1 = '0' else IN2 after 10ns when S0 = '0' and S1 = '1' else IN3 after 10ns;

```

In the above example, the statement is executed any time an event occurs on signals IN0,IN1,IN2,IN3,S0 or S1. The first condition is checked, if it is false, then the second condition is checked, if it even false, then the third condition is checked and so on. Eventually, S0 = '0' and S1 = '1', then the value of IN2 is scheduled to be assigned to signal Z after 10ns.

The next interesting concept in dataflow modeling is **Selected Signal Assignment Statement**. This select different values for a target signal based on the value of a select expression. Whenever an event occurs on a signal in the select expression or on any signal used in any of the waveform expressions, the statement is executed.

#### 7.6.3 Structural Modeling

In structural style of modeling, an entity is described as a set of interconnected components. The top-level design entity's architecture describes the description of lower-level design entities. This is most useful and efficient when a complex system is described as an interconnection of moderately complex design entities. This approach allows each design entity to be independently designed and verified before being used in the higher level description.

There are two major factors to be considered while writing the coding in structural modeling,

- Component declaration

- Component instantiation

Let us consider an example of structural modeling,

library ieee;

use ieee.std\_logic\_1164.all;

entity half\_adder is

port (a, b: in std\_logic;

sum, carry\_out: out std\_logic);

end half\_adder;

architecture structure of half\_adder is

```

component xor_gate

port (i1, i2: in std_logic;

o1: out std_logic);

end component;

component and_gate

port (i1, i2: in std_logic;

o1: out std_logic);

end component;

begin

u1: xor_gate port map (i1 => a, i2 => b, o1 => sum);

u2: and_gate port map (i1 => a, i2 => b, o1 => carry_out);

end structure;

```

In the above example, the program starts with an usual entity which describes the number of signals, that is, input and output ports. Then followed by architecture body which has two separation, one is the component declaration and the another one is the component instantiation part.

The circuit diagram of a half-adder consists of one xor gate and one or gate. So, the major criteria to proceed these gates are first one is component declaration and next one is the component instantiation.

The component declaration of xor gate is

```

component xor_gate

port (i1, i2: in std_logic;

o1: out std_logic);

end component;

```

The component declaration declares the name and the interface of a component. The interface specifies the mode and type of ports.

```

Component instantiation of xor gate is u1: xor_gate port map (i1 => a, i2 => b, o1 => sum);

```

It defines a subcomponent of the entity in which it appears. It associates the signals in the entity with the ports of that subcomponent.

The same way if you take the AND gate, it is also categorized with component declaration and component instantiation in the above half adder program.

# 7.6.4 VHDL delays

In VHDL there are two different kind of delay,

- 1. Transport delay

- 2. Inertial delay

# Transport delay

It is used to model the delay introduced by wire connection or a PCB connection. It is not the default delay implemented in VHDL and must be specified. This delay model is useful to describe delay line, PCB delay, wire delay. This delay represents pure propagation delay; that is, any changes on an input are transported to the output, after the specified delay. The keyword transport must be used in a signal assignment statement.

# For Example

#### b <= transport a after 20ns;

In the above example, **b** takes the value of **a** after 20ns of transport delay. This means that no matter how fast **a** changes his value, **b** will follow the behavior of **a** after the amount of time specified in the delay statement.

#### **Inertial Delay**

The inertial delay model is the default delay implemented in VHDL because it's behavior is very similar to the delay of the device. It models the delays repeatedly found in switching circuits. An input value must be constant for a specified pulse rejection limit duration before the value is allowed to propagate to the output. The value appears at the output after the specified inertial delay. If the input is not stable for the specified limit, no output change occurs. When used with signal assignments, the input value is represented by the value of the expression on the right-hand-side and the output is represented by the target signal. The general form is

signal-object <= [[reject pulse-rejection-limit] inertial]expression after inertial-delay-value;

If no pulse rejection limit is specified, the default pulse rejection limit is the inertial delay value itself. The pulse rejection limit cannot be negative or greater than the value of the inertial delay.

The general form with example is

#### $b \le a$ after 20ns;

In the above example **b** take the value of **a** after 20 ns second of inertial delay. This means that if a value varies faster than 20 ns **b** remain unchanged. At simulation start **a** and **b** are 0; **a** change from 0 to 1, and **b** change its value after 20 ns; then **a** changes value going to 0 and then to 1 in 10 ns.

This delay is less than inertial delay of 20 ns. So b remains unchanged.

VHDL transport and inertial delay model allow the designer to model different type of behavior on VHDL hardware implementation. They are very useful in test bench modeling and in VHDL macro model delay modeling such as RAM, ROM, and peripheral interfacing.

# 7.7 VHDL data types

VHDL is a strongly typed language. This means that every object assumes the value of its nominated type. To put it very simply, the data type of the left-hand side (LHS) and right-hand side (RHS) of a VHDL statement must be the same. The VHDL 1076 specification describes four classes of data types.

- Scalar types represent a single numeric value or, in the case of enumerated types, an enumeration value. The standard types that fall into this class are integer, real (floating point), physical, and enumerated. All of these basic types can be thought of as numeric values.

- Composite types represent a collection of values. There are two classes of composite types: arrays containing elements of the same type, and records containing elements of different types.

- Access types provide references to objects in much the same way that pointer types are used to reference data in software programming languages.

- File types reference objects (typically disk files) that contain a sequence of values.

#### Integer type

The maximum range of a VHDL integer type is  $(2_{31}1)$  to  $2_{31}$ -1. Integer types are defined as subranges of this anonymous built-in type. Multidigit numbers in VHDL can include underscores (\_) to make them easier to read. VHDL Compiler encodes an integer value as a bit vector whose length is the minimum necessary to hold the defined range. VHDL Compiler encodes integer ranges that include negative numbers as 2's-complement bit vectors. The syntax of an integer type definition is

type type\_name is range integer\_range;

type\_name is the name of the new integer type, and integer\_range is a subrange of the anonymous integer type. Example 4–5 shows some integer type definitions.

#### Array type

An array is an object that is a collection of elements of the same type. VHDL supports N-dimensional arrays, but VHDL Compiler supports only one-dimensional arrays. Array elements can be of any type. An array has an index whose value selects each element. The index range determines how many elements are in the array and their ordering (low to high, or high downto low). An index can be of any integer ype. You can declare multidimensional arrays by building one-dimensional arrays where the element type is another one-dimensional array.

## For example

```

type BYTE is array (7 downto 0) of BIT; type VECTOR is array (3 downto 0) of BYTE;

```

#### Record types

A record is a set of named fields of various types, unlike an array, which is composed of identical anonymous entries. A record's field can be of any previously defined type, including another record type.

## Predefined datatypes

IEEE VHDL describes two site-specific packages, each containing a standard set of types and operations: the STANDARD package and the TEXTIO package.

The STANDARD package of data types is included in all VHDL source files by an implicit use clause. The TEXTIO package defines types and operations for communication with a standard programming environment (terminal and file I/O). This package is not needed for synthesis, and therefore VHDL Compiler does not support it.

#### 7.8 VHDL operators

Highest precedence first, left to right within same precedence group, use parenthesis to control order.

Unary operators take an operand on the right.

"result same" means the result is the same as the right operand.

Binary operators take an operand on the left and right.

"result same" means the result is the same as the left operand.

\* multiplication, numeric \* numeric, result numeric / division, numeric / numeric, result numeric mod modulo, integer mod integer, result integer rem remainder, integer rem integer, result integer

+ unary plus, + numeric, result numeric - unary minus, - numeric, result numeric

+ addition, numeric + numeric, result numeric - subtraction, numeric - numeric, result numeric & concatenation, array or element array or element,

sll shift left logical, logical array sll integer, result same srl shift right logical, logical array srl integer, result same sla shift left arithmetic, logical array sla integer, result same sra shift right arithmetic, logical array sra integer, result same rol rotate left, logical array rol integer, result same ror rotate right, logical array ror integer, result same

= test for equality, result is boolean /= test for inequality, result is boolean < test for less than, result is boolean <= test for less than or equal, result is boolean > test for greater than, result is boolean >= test for greater than or equal, result is boolean

and logical and, logical array or boolean, result is same or logical or, logical array or boolean, result is same nand logical complement of and, logical array or boolean, result is same nor logical complement of or, logical array or boolean, result is same xor logical exclusive or, logical array or boolean, result is same xnor logical complement of exclusive or, logical array or boolean, result is same

# 7.8.1 VHDL Functions

The function is a subprogram that either defines an algorithm for computing values or describes a behavior. The important feature of functions is that they are used as expressions that return values of specified type. This is the main difference from another type of subprograms: procedures, which are used as statements.

The result returned by a function can be of either scalar or complex type.

Functions can be either pure (which is default) or impure. Pure functions always return the same value for the same set of actual parameters. Impure

functions may return different values for the same set of parameters. Additionally, an impure function may have side effects", like updating objects outside of their scope, which is not allowed for pure functions.

The function definition consists of two parts:

- function declaration, which consists of name, parameter list and type of the values returned by the function;

- function body, which contains local declarations of nested subprograms, types, constants, variables, files, aliases, attributes and groups, as well as sequence of statements specifying the algorithm performed by the function.

The function declaration is optional and function body, which contains a copy of it, is sufficient for correct specification. However, if a function declaration exists, the function body declaration must appear in the given scope.

#### **Function Declaration**

The function declaration can be preceded by an optional reserved word pure or impure, denoting the character of the function. If the reserved word is omitted it is assumed by default that the function is pure.

The function name, which appears after the reserved word function, can be either an identifier or an operator symbol (if the function specifies the operator). Specification of new functions for existing operators is allowed in VHDL and is called operator overloading. See respective topic for details.

The parameters of the function are by definition inputs and therefore they do not need to have the mode (direction) explicitly specified. Only constants, signals and files can be function parameters. The object class is specified by a reserved word (constant, signal or file, respectively) preceding the parameter's name. If no reserved word is used, it is assumed by default that the parameter is a constant.

In case of signal parameters the attributes of the signal are passed into the function, except for 'STABLE, 'QUIET, 'TRANSACTION and 'DELAYED, which may not be accessed within the function.

If a file parameter is used, it is necessary to specify the type of the data appearing in the opened file.

Example 1 contains several examples of function declarations.

#### **Function Body**

Function body contains a sequence of statements that specify the algorithm to

be realized within the function. When the function is called, the sequence of statements is executed.

A function body consists of two parts: declarations and sequential statements. At the end of the function body, the reserved word end can be followed by an optional reserved word function and the function name. Examples 2 through 4 illustrate the function bodies.

# For example

```

type Int_Data is file of NATURAL; function Func_1 (A,B,X: REAL) return REAL; function "*" (a,b: Integer_new) return Integer_new; function Add_Signals (signal In1,In2: REAL) return REAL; function End_Of_File (file File_name: Int_Data) return BOOLEAN;

```

The first function above is called Func\_1, it has three parameters A, B and X, all of REAL type and returns a value also of REAL type.

The second function defines a new algorithm for executing multiplication. Note that the operator is enclosed in double quotes and plays the role of the function name.

The third function is based on signals as input parameters, which is denoted by the reserved word signal preceding the parameters.

The fourth function declaration is a part of the function checking for end of file, consisting of natural numbers. Note that the parameter list uses the Boolean type declaration.

#### 7.8.2 VHDL procedure

We start our discussion of subprograms with procedures. There are two aspects to using procedures in a model: first the procedure is declared, then elsewhere the procedure is called. The syntax rule for a procedure declaration is

```

subprogram_body

procedure identifier [ ( parameter_interface_list ) ] is

subprogram_declarative_part

begin

{ sequential_statement }

end [ procedure ] [ identifier ] ;

```

The identifier in a procedure declaration names the procedure. The name may be repeated at the end of the procedure declaration. The sequential statements in the body of a procedure implement the algorithm that the procedure is to perform and can include any of the sequential statements that we have seen in previous chapters. A procedure can declare items in its declarative part for use in the statements in the procedure body. The declarations can include types, subtypes, constants, variables and nested subprogram declarations. The items declared are not accessible outside of the procedure; we say they are local to the procedure. The actions of a procedure are invoked by a procedure call statement, which is yet another VHDL sequential statement.

A procedure with no parameters is called simply by writing its name, as shown by the syntax rule

```

procedure_call_statement <= procedure_name ;</pre>

```

When the last statement in the procedure is completed, the procedure returns. We can write a procedure declaration in the declarative part of an architecture body or a process. If a procedure is included in an architecture body's declarative part, it can be called from within any of the processes in the architecture body. On the other hand, declaring a procedure within a process hides it away from use by other processes.

# For example

```

architecture rtl of control_processor is

type func_code is (add, subtract);

signal op1, op2, dest: integer;

signal Z_flag: boolean;

signal func : func_code;

begin

alu: process is

procedure do_arith_op is

variable result: integer;

begin

case func is

when add =<

result := op1 + op2;

when subtract =>

result := op1 - op2;

end case:

dest <= result after Tpd;

Z_{\text{flag}} \le \text{result} = 0 \text{ after Tpd};

end procedure do_arith_op;

begin

do_arith_op;

end process alu;

end architecture rtl:

```

#### 7.8.3 Resolved signals and library

# IEEE Std\_Logic\_1164 Resolved Subtypes

VHDL provides a very general mechanism for specifying what value results from connecting multiple outputs together. It does this through resolved subtypes and resolved signals, which are an extension of the basic signals we have used in previous chapters. However, most designs simply use the resolved subtypes defined in the standard-logic package, std\_logic\_1164. In this tutorial, we will restrict our attention to those subtypes.

```

First, recall that the package provides the basic type std_ulogic, defined as type std_ulogic is ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-'); and an array type std_ulogic_vector, defined as type std_ulogic_vector is array ( natural range <> ) of std_ulogic;

```

We have not mentioned it before, but the "u" in "ulogic" stands for unresolved. Signals of these types cannot have multiple sources. The standard-logic package also provides a resolved subtype called std\_logic. A signals of this type can have multiple sources. The package also declares an array type of standard-logic elements, analogous to the bit\_vector type, for use in declaring array signals:

```

type std_logic_vector is array ( natural range <>) of std_logic;

```

The standard defines the way in which contributions from multiple sources are resolved to yield the final value for a signal. If there is only one driving value, that value is used. If one driver of a resolved signal drives a forcing value ('X', '0' or '1') and another drives a weak value('W', 'L' r 'H'), the forcing value dominates. On the other hand, if both drivers drive different values with the same strength, the result is the unknown value of that strength ('X' or 'W'). The high-impedance value, 'Z', is dominated by forcing and weak values. If a "don't care" value ('L') is resolved with any other value, the result is the unknown value 'X'. The interpretation of the "don't care" value is that the model has not made a choice about its output state. Finally, if an "uninitialized" value ('U') is to be resolved with any other value, the result is 'U', indicating that the model has not properly initialized all outputs.

In addition to this multivalued logic subtype, the package std\_logic\_1164 declares a number of subtypes for more restricted multivalued logic modeling. The subtype declarations are

```

subtype X01 is resolved std_ulogic range 'X' to '1'; — ('X','0','1') subtype X01Z is resolved std_ulogic range 'X' to 'Z'; — ('X','0','1','Z') subtype UX01 is resolved std_ulogic range 'U' to '1'; — ('U','X','0','1') subtype UX01Z is resolved std_ulogic range 'U' to 'Z'; — ('U','X','0','1','Z')

```

The standard-logic package provides the logical operators and, nand, or, nor, xor, xnor and not for standard-logic values and vectors, returning values

in the range 'U', 'X', '0' or '1'. In addition, there are functions to convert between values of the full standard-logic type, the subtypes shown above and the predefined bit and bit-vector types.

# 8 Verilog Content

The standard-logic package provides the logical operators and, nand, or, nor, xor, xnor and not for standard-logic values and vectors, returning values in the range 'U', 'X', '0' or '1'. In addition, there are functions to convert between values of the full standard-logic type, the subtypes shown above and the predefined bit and bit-vector types.

Verilog can be used to describe designs at four levels of abstraction:

- Algorithmic level (much like c code with if, case and loop statements)

- Register transfer level (RTL uses registers connected by Boolean equations).

- Gate level (interconnected AND, NOR etc.).

- Switch level (the switches are MOS transistors inside gates)

The language also defines constructs that can be used to control the input and output of simulation.

Verilog has a C-like syntax. However, it is philosophically different than most programming languages since it is used to describe hardware rather than software. In particular:

- Verilog statements are concurrent in nature; except for code between begin and end blocks, there is no defined order in which they execute. In comparison, most languages like C consist of statements that are executed sequentially; the first line in main() is executed first, followed by the line after that, and so on.

- Synthesizable Verilog code is eventually mapped to actual hardware gates.

Compiled C code, on the other hand, is mapped to some bits in storage that a CPU may or may not execute.

More recently Verilog is used as an input for synthesis programs which will generate a gate-level description (a netlist) for the circuit. Some Verilog constructs are not synthesizable. Also the way the code is written will greatly effect the size and speed of the synthesized circuit. Most readers will want to synthesize their circuits, so nonsynthesizable constructs should be used only for test benches. These are program modules used to generate I/O needed to simulate

the rest of the design. The words "not synthesizable" will be used for examples and constructs as needed that do not synthesize.

There are two types of code in most HDLs: Structural, which is a verbal wiring diagram without storage. assign  $a=b\ c-d;$  /\* "—" is a OR \*/ assign  $d=e\ (c);$

Here the order of the statements does not matter. Changing e will change a. Procedural which is used for circuits with storage, or as a convenient way to write conditional logic.

always @(posedge clk) // Execute the next statement on every rising clock edge. count <= count+1;

Procedural code is written like c code and assumes every assignment is stored in memory until over written. For synthesis, with flip-flop storage, this type of thinking generates too much storage. However people prefer procedural code because it is usually much easier to write, for example, if and case statements are only allowed in procedural code. As a result, the synthesizers have been constructed which can recognize certain styles of procedural code as actually combinational. They generate a flip-flop only for left-hand variables which truly need to be stored. However if you stray from this style, beware. Your synthesis will start to fill with superfluous latches.

Verilog source text files consists of the following lexical tokens:

- 1. White Space White spaces separate words and can contain spaces, tabs, new-lines and form feeds. Thus a statement can extend over multiple lines without special continuation characters.

- 2. Comments Comments can be specified in two ways (exactly the same way as in C/C++):

- Begin the comment with double slashes (//). All text between these characters and the end of the line will be ignored by the Verilog compiler.

- Enclose comments between the characters /\* and \*/. Using this method allows you to continue comments on more than one line. This is good for "commenting out" many lines code, or for very brief in-line comments.

- 3. Numbers Number storage is defined as a number of bits, but values can be specified in binary, octal, decimal or hexadecimal. Examples are 3'b001, a 3-bit number, 5'd30, (=5'b11110), and 16'h5ED4, (=16'd24276)

- 4. Identifiers Identifiers are user-defined words for variables, function names, module names, block names and instance names. Identifiers begin with a letter or underscore (Not with a number or \$) and can include any number of letters, digits and underscores. Identifiers in Verilog are case-sensitive.

- 5. Operators Operators are one, two and sometimes three characters used to perform operations on variables. Examples include >, +, ,, !=.

6. Verilog Keywords - These are words that have special meaning in Verilog. Some examples are assign, case, while, wire, reg, and, or, nand, and module. They should not be used as identifiers.

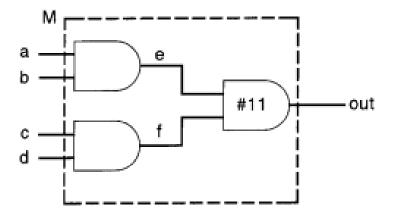

# 8.1 Gate-level Modelling

Primitive logic gates are part of the Verilog language. Two properties can be specified, drive\_strength and delay. Drive\_strength specifies the strength at the gate outputs. The strongest output is a direct connection to a source, next comes a connection through a conducting transistor, then a resistive pull-up/down. The drive strength is usually not specified, in which case the strengths defaults to strong1 and strong0. Delays: If no delay is specified, then the gate has no propagation delay; if two delays are specified, the first represent the rise delay, the second the fall delay; if only one delay is specified, then rise and fall are equal. Delays are ignored in synthesis. This method of specifying delay is a special case of "Parameterized Modules"

# 8.1.1 Basic gates

These implement the basic logic gates. They have one output and one or more inputs. In the gate instantiation syntax shown below, GATE stands for one of the keywords and, nand, or, nor, xor, xnor.

## Syntax

```

GATE (drive_strength) (delays) instance_name1(output, input_1, input_2,..., input_N), instance_name2(outp,in1, in2,..., inN);

Delays is (rise, fall) or rise_and_fall or (rise_and_fall)

```

## 8.1.2 buf,not Gates

These implement buffers and inverters, respectively. They have one input and one or more outputs. In the gate instantiation syntax shown below, GATE stands for either the keyword buf or not

# Syntax

```

GATE (drive_strength) (delays) instance_name1(output_1, output_2, ..., output_n, input), instance_name2(out1, out2, ..., outN, in);

```

# 8.1.3 Three-State Gates; bufif1, bufif0, notif1, notif0

These implement 3-state buffers and inverters. They propagate z (3-state or high-impedance) if their control signal is deasserted. These can have three delay specifications: a rise time, a fall time, and a time to go into 3-state.

# 8.2 Data Types

## 8.2.1 Valueset

Verilog consists of only four basic values. Almost all Verilog data types store all these values:

- 0 (logic zero, or false condition)

- 1 (logic one, or true condition)

- x (unknown logic value) x and z have limited use for synthesis.

- z (high impedance state)

## 8.2.2 Wire

A wire represents a physical wire in a circuit and is used to connect gates or modules. The value of a wire can be read, but not assigned to, in a function or block. See "Functions" on p. 19, and "Procedures: Always and Initial Blocks" on p. 18. A wire does not store its value but must be driven by a continuous assignment statement or by connecting it to the output of a gate or module. Other specific types of wires include:

wand (wired-AND);:the value of a wand depend on logical AND of all the drivers connected to it.

wor (wired-OR);: the value of a wor depend on logical OR of all the drivers connected to it.

tri (three-state;): all drivers connected to a tri must be z, except one (which determines the value of the tri)

#### **Syntax**

wire [msb:lsb] wire\_variable\_list; wand [msb:lsb] wand\_variable\_list; wor [msb:lsb] wor\_variable\_list; tri [msb:lsb] tri\_variable\_list;

# 8.2.3 Reg

Declare type reg for all data objects on the left hand side of expressions in inital and always procedures, or functions. See "Procedural Assignments" on page 12. A reg is the data type that must be used for latches, flip-flops and memory. However it often synthesizes into leads rather than storage. In multi-bit registers, data is stored as unsigned numbers and no sign extension is done for what

the user might have thought were two's complement numbers.

# Syntax

reg [msb:lsb] reg\_variable\_list;

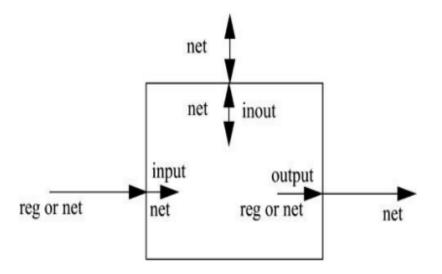

# 8.2.4 Input,Output and Inout

These keywords declare input, output and bidirectional ports of a module or task. Input and inout ports are of type wire. An output port can be configured to be of type wire, reg, wand, wor or tri. The default is wire.

# **Syntax**

```

input [msb:lsb] input_port_list;

output [msb:lsb] output_port_list;

inout [msb:lsb] inout_port_list;

```

## 8.2.5 Integer

Integers are general-purpose variables. For synthesois they are used mainly loops-indicies, parameters, and constants. They are of implicitly of type reg. However they store data as signed numbers whereas explicitly declared reg types store them as unsigned. If they hold numbers which are not defined at compile time, their size will default to 32-bits. If they hold constants, the synthesizer adjusts them to the minimum width needed at compilation.

# Syntax

```

integer integer_variable_list;

... integer_constant ...;

```

# 8.2.6 Supply0, Supply1

Supply0 and supply1 define wires tied to logic 0 (ground) and logic 1 (power), respectively.

#### **Syntax**

```

supply0 logic_0_wires;

supply1 logic_1_wires;

```

#### 8.2.7 Time

Time is a 64-bit quantity that can be used in conjunction with the \$time system task to hold simulation time. Time is not supported for synthesis and hence is used only for simulation purposes.

# Syntax

time time\_variable\_list;

#### 8.2.8 Parameter

Parameters allows constants like word length to be defined symbolically in one place. This makes it easy to change the word length later, by change only the parameter.

# **Syntax**

```

parameter par_1 = value,

par_2 = value, .....;

parameter [range] parm_3 = value

```

# 8.3 Operators

# 8.3.1 Arithmetic Operators

These perform arithmetic operations. The + and - can be used as either unary (-z) or binary (x-y) operators.

```

Operators

+ (addition)

- (subtraction)

(multiplication)

/ (division)

% (modulus)

```

# 8.3.2 Relational Operators

Relational operators compare two operands and return a single bit 1 or 0. These operators synthesize into comparators. Wire and reg variables are positive Thus (-3'b001) = 3'b111 and (-3d001) > 3d110. However for integers -1 < 6.

```

< (less than)

<= (less than or equal to)

> (greater than)

>= (greater than or equal to)

== (equal to)

!= (not equal to)

```

# 8.3.3 Bit-wise Operators

Bit-wise operators do a bit-by-bit comparison between two operands.

```

\sim (bitwiseNOT) & (bitwiseAND) | (bitwiseOR) \land (bitwiseXOR) \land or \land \sim (bitwiseXNOR)

```

# 8.3.4 Logical Operators

Logical operators return a single bit 1 or 0. They are the same as bit-wise operators only for single bit operands. They can work on expressions, integers or groups of bits, and treat all values that are nonzero as "1". Logical operators are typically used in conditional (if ... else) statements since they work with expressions.

```

! (logical NOT) && (logical AND) || (logical OR)

```

## 8.3.5 Reduction Operators

Reduction operators operate on all the bits of an operand vector and return a single-bit value. These are the unary (one argument) form of the bit-wise operators above.

```

& (reduction AND)

| (reductionOR)

\sim \&(reductionNAND)

\sim | |(reductionNOR)

\wedge (reductionXOR)

\sim \land or \land \sim (reductionXNOR)

```

#### 8.3.6 Shift Operators

Shift operators shift the first operand by the number of bits specified by the second operand. Vacated positions are filled with zeros for both left and right shifts (There is no sign extension).

```

<< (shift left)

>> (shift right)

```

# 8.3.7 Concatenation Operator

The concatenation operator combines two or more operands to form a larger vector.

${n\{\text{item}\}}\ (\text{n fold replication of an item})$

# 8.3.8 Conditional Operator: "?"

Conditional operator is like those in C/C++. They evaluate one of the two expressions based on a condition. It will synthesize to a multiplexer (MUX).

(cond) ? (result if cond true): (result if cond false)

# 8.3.9 Operator Precedence

The following table shows the precedence of operator from highest to lowest. Operators on the same level evaluate from left to right. It is strongly recommended to use parentheses to define order of precedence and improve the readability of your code.

| Operator                | Name                                                                                                                                   |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| []                      | bit-select or part-select                                                                                                              |

| ()                      | parenthesis                                                                                                                            |

| !, ~                    | logical and bit-wise NOT                                                                                                               |

| &,  , ~&, ~ , ^, ~^, ^~ | reduction AND, OR, NAND, NOR, XOR, XNOR;<br>If X=3'B101 and Y=3'B110, then X&Y=3'B100, X^Y=3'B011;                                     |

| +, -                    | unary (sign) plus, minus; +17, -7                                                                                                      |

| { }                     | concatenation; {3'B101, 3'B110} = 6'B101110;                                                                                           |

| {{ }}                   | replication; {3{3'B110}} = 9'B110110110                                                                                                |

| *, /, %                 | multiply, divide, modulus; \(\lambda \text{and \% not be supported for synthesis}\)                                                    |

| +, -                    | binary add, subtract.                                                                                                                  |

| <<, >>                  | shift left, shift right; X<<2 is multiply by 4                                                                                         |

| <, <=, >, >=            | comparisons. Reg and wire variables are taken as positive numbers.                                                                     |

| ==, !=                  | logical equality, logical inequality                                                                                                   |

| ===,!==                 | case equality, case inequality; not synthesizable                                                                                      |

| &                       | bit-wise AND; AND together all the bits in a word                                                                                      |

| ^, ~^, ^~               | bit-wise XOR, bit-wise XNOR                                                                                                            |

| 1                       | bit-wise OR; AND together all the bits in a word                                                                                       |

| &&,                     | logical AND. Treat all variables as False (zero) or True (nonzero). logical OR. $(7  0)$ is $(T  F) = 1$ , $(2  -3)$ is $(T  T) = 1$ , |

|                         | (3&&0) is $(T\&\&F) = 0$ .                                                                                                             |

| ?:                      | conditional. x=(cond)? T:F;                                                                                                            |

# 8.4 Design Methodologies

There are two basic types of digital design methodologies: a top-down design methodology and a bottom-up design methodology.

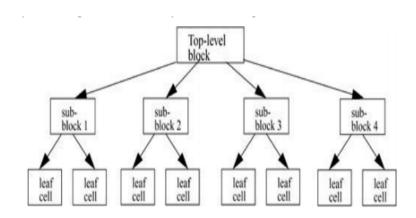

# 8.4.1 Top-down design methodology

This designing approach allows early testing, easy change of different technologies, a well structures system design and offers many other advantages.

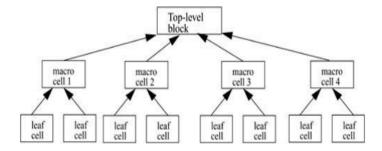

In this method, top-level block is defined and sub-blocks necessary to build the top-level block are identified. We further subdivide, sub-blocks until cells cannot be further divided, we call these cells as leaf cells.

# 8.4.2 Bottom-up design methodology:

We first identify the available building blocks and try to build bigger cells out of these, and continue process until we reach the top-level block of the design. Most of the time, the combination of these two design methodologies are used to design. Logic designers decide the structure of design and break up the functionality into blocks and sub blocks. And designer will design a optimized circuit for leaf cell and using these will design top level design.

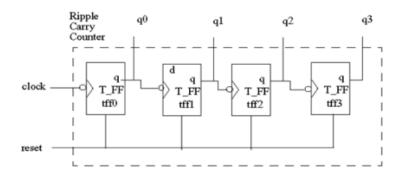

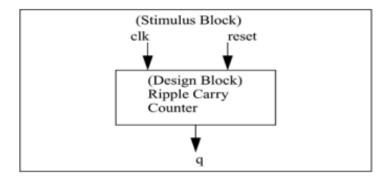

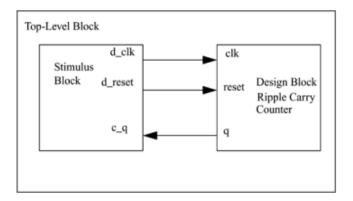

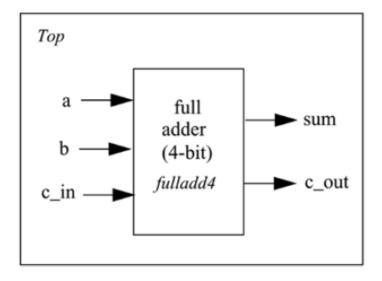

A hierarchical modeling concept is illustrated with an example of 4-bit Ripple Carry Counter. The ripple carry counter is made up of negative edge-triggered toggle flip-flops (T\_FF). Each of the T\_FFs can be made up from negative edge-triggered D-flipflops (D\_FF) and inverters

6.

Thus, the ripple carry counter is built in a hierarchical fashion by using building blocks.

In a top-down design methodology, we first have to specify the functionality of the ripple carry counter, which is the top-level block. Then, we implement the counter with T\_FFs. We build the T\_FFs from the D\_FF and an additional inverter gate. Thus, we break bigger blocks into smaller building sub-blocks until we decide that we cannot break up the blocks any further. A bottom-up methodology flows in the opposite direction. We combine small building blocks and build bigger blocks; e.g., we could build D\_FF from and/ or gates, or we could build a custom D\_FF from transistors. Thus, the bottom-up flow meets the top-down flow at the level of the D\_FF.

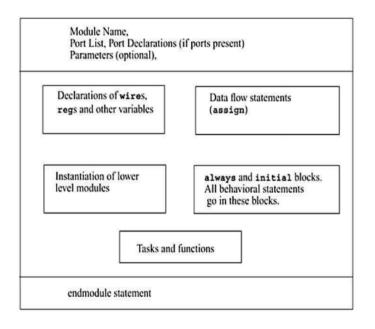

# 8.5 Modules

Verilog provides the concept of a module. A module is the basic building block in Verilog. A module can be an element or a collection of lower-level design blocks. Typically, elements are grouped into modules to provide common functionality